Что строится в современных компьютерах на основе триггеров

Содержание урока

§23. Предикаты и кванторы

§24. Логические элементы компьютера

Триггер

§25. Логические задачи

§24. Логические элементы компьютера

Триггер

1 В английском языке триггер называется flip-flop.

В современных компьютерах на основе триггеров строится быстродействующая оперативная память. Один триггер способен хранить один бит данных. Соответственно, для того, чтобы запомнить 1 байт информации, требуется 8 триггеров, а для хранения 1 килобайта данных — 8 • 1024 = 8192 триггера.

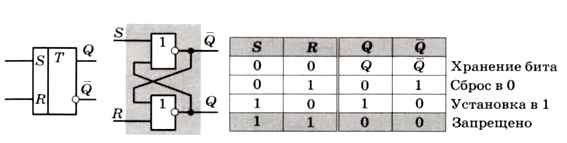

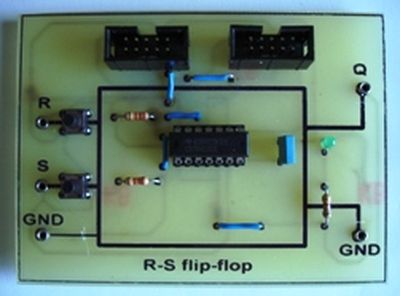

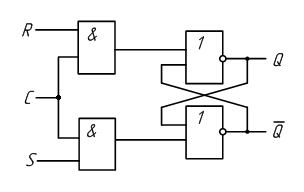

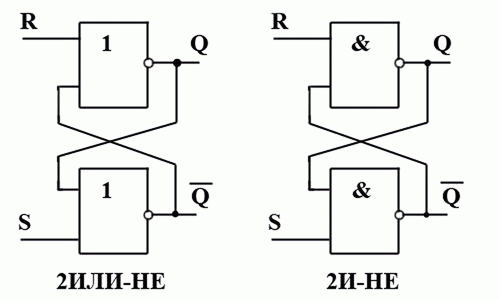

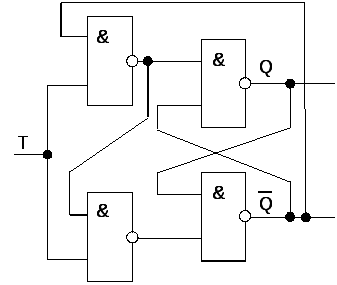

RS-триггер можно построить на двух элементах «И-НЕ» или на двух элементах «ИЛИ-HE». На рисунке 3.26 показано условное обозначение RS-триггера, внутреннее устройство триггера на элементах «ИЛИ-HE» и его таблица истинности.

Триггер использует так называемые обратные связи — сигналы с выходов схем «ИЛИ-HE» поступают на вход соседней схемы. Именно это позволяет хранить информацию.

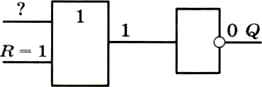

Построим таблицу истинности триггера. Начнем с варианта, когда S = 0 и R = 1. Элемент «ИЛИ-HE» в нижней части схемы можно заменить на последовательное соединение элементов «ИЛИ» и «НЕ». Независимо от второго входа, на выходе «ИЛИ» будет 1, а на выходе «НЕ» — ноль. Это значит, что Q = 0 (рис. 3.27).

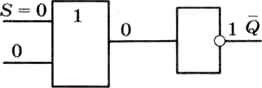

Тогда на входе другого элемента «ИЛИ-HE» будут два нуля, а на выходе Q — единица (рис. 3.28).

Поскольку основным выходом считается Q, мы записали в триггер значение 0. Схема симметрична, поэтому легко догадаться, что при S = 1 и R = 0 мы запишем в триггер 1 (Q = 1).

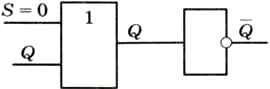

Теперь рассмотрим случай, когда S = 0 и R = 0. На входе первого элемента «ИЛИ» будет сигнал Q + 0 = Q, поэтому на выходе Q останется его предыдущее значение (рис. 3.29).

Аналогично легко показать, что на выходе Q тоже остаётся его предыдущее значение. Это режим хранения бита.

Для случая S = 1 и R = 1 мы увидим, что оба выхода становятся равны нулю — в этом нет смысла, поэтому такой вариант запрещён.

Для хранения многоразрядных данных триггеры объединяются в единый блок, который называется регистром. Регистры (размером от 8 до 64 битов) используются во всех процессорах для временного хранения промежуточных результатов.

Над регистром, как над единым целым, можно производить ряд стандартных операций: сбрасывать (обнулять), заносить в него код и т. д. Часто регистры способны не просто хранить информацию, но и обрабатывать её. Например, существуют регистры- счётчики, которые подсчитывают количество импульсов, поступающих на вход.

Следующая страница

Cкачать материалы урока

Тест с ответами: “Логические элементы”

1. На основе логических элементов ИЛИ и НЕ строится:

а) стрелка Пирса +

б) штрих Шеффера

в) исключающее ИЛИ

2. Если проинвертировать выход логического элемента И, то получится элемент под названием:

а) исключающее ИЛИ

б) штрих Шеффера +

в) стрелка Пирса

3. Для какого логического элемента справедливо высказывание «Результат этой операции равен нулю в том случае, когда на входы подаются нули. В остальных случаях результат всегда равен единице»:

а) И-НЕ

б) ИЛИ-НЕ

в) ИЛИ +

4. Для какого логического элемента справедливо высказывание «Результат равен 1 только в том случае, когда на входы данного элемента подаются две единицы. Во всех остальных случаях результат равен нулю»:

а) И +

б) ИЛИ

в) ИЛИ-НЕ

5. Какой из логических элементов имеет один вход и один выход:

а) конъюнкция

б) дизъюнкция

в) инверсия +

6. Для чего необходим сумматор:

а) для вычитания третичных чисел

б) для сложения двоичных чисел +

в) для сложения дробей

7. Какой объем данных способен хранить один триггер:

а) четыре бита

б) два бита

в) один бит +

8. Что строится в современных компьютерах на основе триггеров:

а) быстродействующая оперативная память +

б) винчестер

в) жесткий диск

9. Кто из ученых изобрел триггер:

а) Маркони

б) Роуз

в) Бонч-Бруевич +

10. Кто из ученых изобрел триггер:

а) Маркони

б) Икклз +

в) Роуз

11. Кто из ученых изобрел триггер:

а) Джордан +

б) Линней

в) Попов

12. Когда была изобретена схема «триггер»:

а) в 1920 году

б) в 1918 году +

в) в 1910 году

13. Как называется электронная схема, которая может находиться только в двух состояниях:

а) Триггер +

б) Пиксель

в) Домен

14. Из какого языка заимствовано слово «триггер»:

а) французского

б) немецкого

в) английского +

15. Как называются электронные схемы, выполняющие логические операции:

а) логические элементы +

б) ключи

в) формулы

16. Как строят схему по известному логическому выражению:

а) с середины

б) с конца +

в) с начала

17. Как переводится слово «триггер»:

а) «Точка»

б) «Ключ»

в) «Защелка» +

18. Устройство, выполняющее одну из логических операций:

а) логический метод

б) логический элемент +

в) логический способ

19. Что такое регистр:

а) устройство для визуального контроля

б) манипулятор для ПК

в) совокупность триггеров +

20. Чем оперирует триггер:

а) короткими сигналами, поступающих хаотично

б) значениями двоичного кода +

в) логическими уравнениями

21. Чем оперирует регистр:

а) триггерами и значениями в них +

б) сигналами

в) двоичным кодом

22. Один из видов регистра:

а) второстепенный

б) последовательный +

в) главный

23. Один из видов регистра:

а) основной

б) дополнительный

в) параллельный +

24. Один из видов регистра:

а) дополнительный

б) последовательно-параллельный +

в) придаточный

25. Какое количество информации может хранить триггер:

а) 1 байт

б) до одного терабайта

в) 1 бит +

26. Регистр, в котором осуществляется сдвиг числа называется:

а) сдвинутым регистром

б) регистр сдвига +

в) устройством ввода тока

27. Что используют для уплотнения каналов связи:

а) мультиплексоры +

б) счетчики

в) резисторы

28. Как называется устройство, реализующее одну из логических операций:

а) дизьюнктор

б) счетчики

в) логический элемент +

29. Каким кодом осуществляется выбор входа по его номеру мультиплексор:

а) двоичным +

б) десятеричным

в) восьмеричным

30. Вычислительная машина, которая обрабатывает информацию, представленную в аналоговой форме:

а) счетная машина

б) аналоговая вычислительная машина +

в) коммутатор

Основные функциональные элементы ЭВМ, часть 1

Триггер

Триггеры служат основой для построения регистров, счетчиков и других элементов, обладающих функцией хранения.

Главной частью любого триггера является запоминающая ячейка (ЗЯ). Схема запоминающей ячейки на элементах «И-НЕ» представлена на рис. 1.5.

Если на входы S и R поданы сигналы низкого уровня ( S = R = 0 ), то сигнал на выходах элементов 1 и 2 будет высоким ( Q = Q = 1 ). При переводе ЗЯ в режим хранения ( S = R = 1 ), выходы элементов 1 и 2 могут установиться в произвольное состояние. Поэтому комбинация сигналов S = R = 0 на управляющих входах не используется.

Работа триггерной схемы определяется не таблицей истинности, как для комбинационной логической схемы, а таблицей переходов. Таблица переходов показывает изменение состояния триггера при изменении состояния входных сигналов в зависимости от его текущего состояния. Таблица переходов запоминающей ячейки, показанной на рис. 1.5, представлена в табл. 1.3.

| S | R | Q(t+1) | Функция |

|---|---|---|---|

| 0 | 0 | х | Запрещенная комбинация |

| 0 | 1 | 1 | Установка в » 1 « |

| 1 | 0 | 0 | Установка в » 0 « |

| 1 | 1 | Q(t) | Хранение |

Аналогичная запоминающая ячейка может быть построена на элементах «ИЛИ-НЕ».

Триггеры можно классифицировать по различным признакам, например так, как это показано на рис. 1.6.

Триггер называется синхронным, если его таблица переходов хотя бы по одному управляющему входу реализуется под воздействием синхронизирующего сигнала.

Рассмотрим организацию синхронного одноступенчатого триггера ( рис. 1.7).

Схема синхронного одноступенчатого RS-триггера приведена на рис. 1.8. Его таблица переходов представлена в табл. 1.4.

| R | S | Q(t+1) | Функция |

|---|---|---|---|

| 0 | 0 | Q(t) | Хранение |

| 0 | 1 | 1 | Установка в » 1 « |

| 1 | 0 | 0 | Установка в » 0 « |

| 1 | 1 | х | Запрещенная комбинация |

| J | K | Q(t+1) | Функция |

|---|---|---|---|

| 0 | 0 | Q(t) | Хранение |

| 0 | 1 | 0 | Установка в » 0 « |

| 1 | 0 | 1 | Установка в » 1 « |

| 1 | 1 | Q(t) | Инвертирование предыдущего состояния |

На рис. 1.9,б представлено УГО триггера со статической синхронизацией в случае, если активный уровень синхросигнала низкий. Условно-графические обозначения триггеров с динамической синхронизацией показаны на рис. 1.9,в и 1.9,г. В первом случае изменение состояния триггера под воздействием поступивших управляющих сигналов происходит только в момент переключения синхронизирующего сигнала с низкого уровня на высокий, а во втором – при переключении с высокого на низкий уровень. При постоянном значении уровня синхросигнала состояние выхода триггера с динамической синхронизацией не меняется при любых изменениях управляющих сигналов на его входах.

Идеализированная (без учета задержек) временная диаграмма работы RS-триггеров с различными типами синхронизации приведена на рис. 1.10.

Что такое триггер

Чтобы узнать, что такое триггер и разобраться во всём, что касается этих устройств, нужно начать с понятия. Слово «Триггер» произошло от английского «trigger» и обозначает цифровое устройство, который имеет только два состояния – 0 и 1. Переход от одного значения к другому происходит с огромной скоростью, и временем этих переходов обычно пренебрегают.

Триггер – это основной элемент системы большинства запоминающих устройств. Они могут быть использованы для хранения информации. Но объём памяти крайне мал, так что там можно держать разве что коды, биты и сигналы.

Память свою триггеры могут сохранять только при наличии питающего напряжения. Из этого следует, что их всё-таки стоит относить к оперативной памяти. Перезапустить питающее напряжение – и триггер будет в одном из двух состояний. То есть иметь или логический ноль, или логическую единицу, и состояние это будет выбрано случайно. Исходя из этой особенности, при проектировании схемы нужно заранее обозначить, как триггер будет возвращаться в стартовое состояние.

Схема, состоящая из двух логических состояний «И-НЕ» или «ИЛИ-НЕ», которые охвачены обратной положительной связью, лежит в основе построения всех триггеров. При подключении схема может пребывать только в одном из двух устойчивых состояний. Если не будет никаких сигналов, то триггер будет сохранять именно заданное состояние и не менять его, пока будет питание.

Триггерные ячейки

Схема имеет два инверсионных входа: Сброс – R (Reset) и установка S (Set). Так же имеются два выхода: Q – прямой и –Q – инверсный. Чтобы триггерная ячейка работала правильно, должно выполниться одно правило. На выходы ячейки не могут в один момент поступить отрицательные импульсы.

На выход –R поступает импульс при одном сигнале на вход –S. Выход –Q тогда оказывается в состоянии «1», выход Q будет в состоянии «0». Обратная связь создаёт переход сигнала «0» на второй вход на нижнем элементе. Когда поступление сигнала на –R прекратится, состояние сигналов на выходах будет тем же – Q (0), –Q (1). Таким образом, схема будет находиться в состоянии стабильности, потому что при подаче импульса на –R, состояние на выходе не изменится.

Одновременно подав на каждый вход сигналы, на каждом выходе в течение их действия и будет по одному сигналу. Как только подача импульсов прекратится, выходы сами перейдут в одно из двух возможных состояний. Это произойдёт случайно. Триггерная ячейка при включении выберет себе одно из двух устойчивых положений. Так же случайно.

Входы и виды триггеров

В зависимости от структуры и выполняемых им функций можно определить число входов триггера.

По параметру записи информации триггеры можно разделить на:

В цифровой схемотехнике обычно можно найти следующие обозначения входов триггера:

Что касается функций, то в этом плане триггеры можно разделить на:

RS- триггер

Это самый простой тип триггеров. На его основе создаются и другие типы. Возможные логические элементы в его построении – это 2И-НЕ (инверсионный вход) и 2ИЛИ-НЕ (прямые входы).

Из-за низкой помехоустойчивости такие триггеры почти не используются самостоятельно. Их можно применить, например, для устранения влияния дребезжащих контактов, которое возникает при коммутации механических переключателей. Тогда требуется тумблер с тремя выходами, один из которых подключается по очереди к остальным двум. Чтобы создать RS-триггер используется D-триггер с замкнутыми на состоянии «ноль» входы С и D.

Первый отрицательный сигнал на входе –R переводит в состояние «0». Первый отрицательный сигнал на входе –S переводит в состояние «1». Другие сигналы, возникшие из-за дребезга контактов, не могут оказать влияние на триггер. При таком подключении переключателя верхнее положение будет равно «1» на выходе, нижнее – «0».

RS-триггер сам по себе асинхронный, однако, иногда возникают случаи, когда нужно сохранить информацию. Тогда на помощь приходит синхронизируемый RS-триггер, который в этом случае должен состоять из обычного RS-триггера и схемы управления.

При этой схеме, импульсы, поступающие на Х1 и Х2 не имеют никакого значения, пока на входе С сохраняет значение «0». В этот момент RS-триггер находится в режиме хранения информации. Как только значение C становится равно «1» триггер запускается, начинается запись.

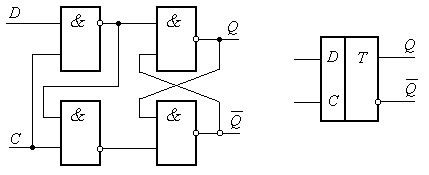

D-триггер

Это триггеры задержки. Используются они для создания регистров сдвига и хранения. Это одна из важнейших частей всех микропроцессоров.

У такого триггера два выхода – информационный и синхронизирующий. Триггер стабилен, когда состояние С находится на «ноль». При этом сигнал на выходе не будет зависеть от сигналов, которые поступают на информационный вход. Когда значение С изменяется на «1» на прямом выходе, тогда информация будет такой же, как и на триггере D.

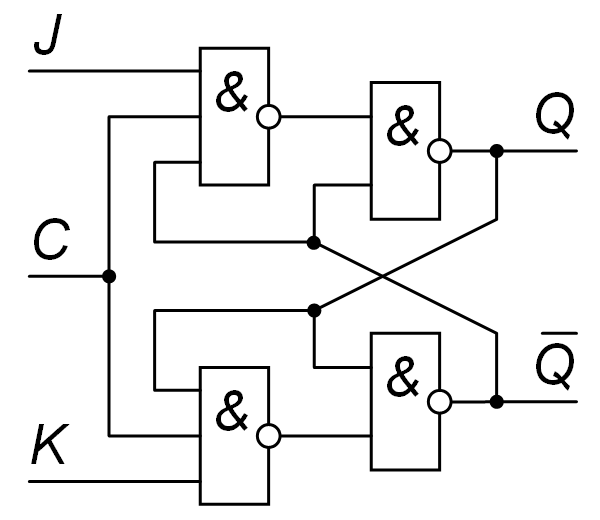

JK-триггер

По своему принципу действия он очень похож на RS- триггеры. Но в отличие от него, у JK-триггеров нет проблем с неопределённостью, когда на вход одновременно поступают две «единицы». При возникновении подобной ситуации JK-триггер становится счётным триггером. Тогда при поступлении на вход сигналов со значением «1» триггер меняет своё состояние на противоположное.

Эти устройства очень универсальны. С одной стороны, они прекрасно находят своё применение в цифровых устройствах – счётчиках, регистрах, делителях частоты и т.д. С другой стороны при соединении определённых выводов можно получить вообще любой нужный вид триггера.

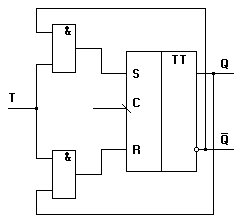

Т-триггер

У этих триггеров есть и другое название – счётные. На их основе создаёт двоичные счётчики и делители частот. У этих триггеров вход только один. На изображениях – асинхронный (1) и синхронный (2) Т-триггеры.

Импульс поступает на этот вход, состояние его меняется не противоположное. После поступления следующего импульса состояние становится исходным.

Триггер переключается в тот момент, когда на его вход поступается синхроимпульс. Тогда частота импульсов на выходе оказывается в 2 раза меньше начальной. Таким образом, один счётный триггер уменьшает частоту импульса двукратно. А два триггера, что были подключены последовательно, логично уменьшат частоту уже в 4 раза.

Почему эти триггеры называют ещё и делителями частот хорошо заметно по временным схемам:

Практическое использование триггера

Об одном из способов использования триггеров уже было сказано выше. Это устранение дребезга контактов. Тогда использовался RS-триггер. Но это далеко не все области, в которых могут применяться эти устройства.

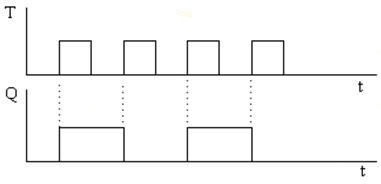

Создание сигнала

Триггеры часто используют, чтобы создать сигнал. Его длительность должна соответствовать длительности какой-нибудь операции в схеме. В этом случае триггер будет служить сигналом, который разрешает начать процесс. А так же он информирует другие устройства, что процесс запущен. В таких случаях триггер называется «флаг процесса».

В момент прихода сигнала в начало процесса триггер переходит в состояние «единицы». Это оповещает о том, что процесс запустился. Когда происходит стоп-сигнал, триггер получает значение «ноль» и процесс завершается.

Как самый простой вариант можно использовать –S и –R входы. Однако, тут всегда будет возможность получить неопределённость, когда сигналы будут на обоих входах. Избежать этой ситуации можно легко. Нужно взять пары входов –R и С и С и –S. Тогда, используя –R и С, на D нужно подать «1». С и –S в использовании требуют «ноль» на D.

В чём удобство такого способа? В том, что сигналы «Стоп» и «Старт» используются не только как уровни, но и фронт сигнала.

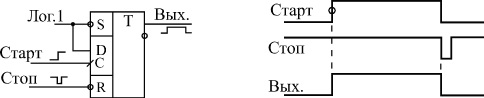

Синхронизация сигналов

Своё применение триггеры так же нашли в области синхронизации сигналов. С помощью устройства можно избавляться от ненужных коротких импульсов. Они возникают на выходе схемы, если вводные сигналы меняют одновременно. Тогда для синхронизации нужен синхросигнал. Он находится в сопровождении у информационных входных сигналов и задержан на время задержки относительно момента, когда изменение входных сигналов только началось. Когда синхросигнал подаётся на вход С, а выходной – на D (у этого же триггера), то сигнал на выходе будет без лишних импульсов.

Разработка цифровых схем так же не обходится без триггеров. Работа этих схем синхронизируется с общим тактовым генератором. И не редко появляется проблема с синхронизацией внешнего сигнала, который поступает на схему и самой схемой. То есть, нужно обеспечить изменение внешнего сигнала, чтобы в результате он менялся с тактами генератора. Внешний сигнал по отношению к тактовому сигналу в схеме – асинхронный. Так что, если совсем простыми словами, сигнал из асинхронного должен стать синхронным для всей схемы.

Эту задачу и решает триггер.

Внешний сигнал создаёт разрешение или запрет на прохождение сигнала, который генерируется тактовым генератором. Если речь идёт о RC-триггере, то нужно просто отключать и включать генератор вовремя. Этот способ кажется простейшим. Однако, это заблуждение. Для начала, выключить и выключить генератор не получится в один момент – ему нужно время и качество сигнала в это время будет далеко от идеала.

Например, генераторы из кварца. Их вовсе не рекомендуется часто останавливать и запускать. После возобновления генератор будет формировать сигнал с задержкой до 5 периодов тактовой частоты. И задержка при каждом включении будет разной.

Также возможность прекращать работу генератора иногда вовсе не существует. Например, если от его работы зависит работа всей схемы.

Для упрощения считают, что тактовый генератор работает не прекращая. Внешний управляющий сигнал тогда будет отвечать за прохождение или блокировку импульсов, которые были сгенерированы.

Самое лёгкое решение – создать процесс запрета и пропуска импульсов, которые генератор создаёт, используя при этом логический элемент 2И. Правда, тут очень большая вероятность, что на выход будут приходить короткие импульсы или с не полной длительностью. Такие сигналы могут оказать плохое влияние на систему в целом, создав неопределённость в функционировании.

В этом случае, синхронизирующий триггер на выходе пропускающего элемента 2И обеспечит только нужные импульсы. То есть те, которые имеют полную длительность. Когда через триггер проходит разрешающий сигнал, он синхронизируется с тактовым сигналом. И на выходе будет целое число тактовых импульсов и целое число периодов, которое задаётся генератором.

Создание задержки

Триггеры так же можно использовать для задержки цифровых сигналов. В этом случае несколько триггеров с общим тактовым сигналом С нужно соединить в цепь. Соединение должно быть последовательным. При включении комбинации схем смогут одновременно обработать несколько состояний одного и того же сигнала.